RDL用硫酸銅めっきプロセス TIPHARES RDP

総合研究所 電子技術開発部 今長谷 昂平 Kohei IMAHASE 小林 玲斗 Reito KOBAYASHI 江田 哲朗 Tetsuro EDA

はじめに

ムーアの法則が限界に近づく中、これまで1つのシリコンダイで構成されていた半導体チップを分割(チップレット)し、複数の半導体チップを1つのパッケージに集積させる後工程の技術が近年注目されている。Interposerは、分割したチップ同士を高密度に接続する役割を持っており、半導体の高速化や省電力化を可能とする重要な部材である。Interposerの素材として配線形成や大面積化が容易、かつ比較的伝送損失が小さな有機材料での検討が進んでおり、FO-WLPやFO-PLPの再配線層Redistribution Layer(以下RDL)技術を応用した

RDL Interposerが注目されている。

従来のFO-WLPなどに用いられるRDLは、パッケージ基板などの有機基板とチップの接続を担う一方、RDL Interposerはチップ同士の接続が主な役割である。そのため、RDL Interposerの配線幅やBVHサイズはより微細なものになるため、微細配線部に対する高い面内均一性が求められる。

今回紹介するTIPHARES RDP(以下RDP)は薄膜でのパターン面内均一性および小径BVHへの優れたフィリング性を有するプロセスであり、RDL Interposerの配線形成向けに適した製品である。

面内均一性

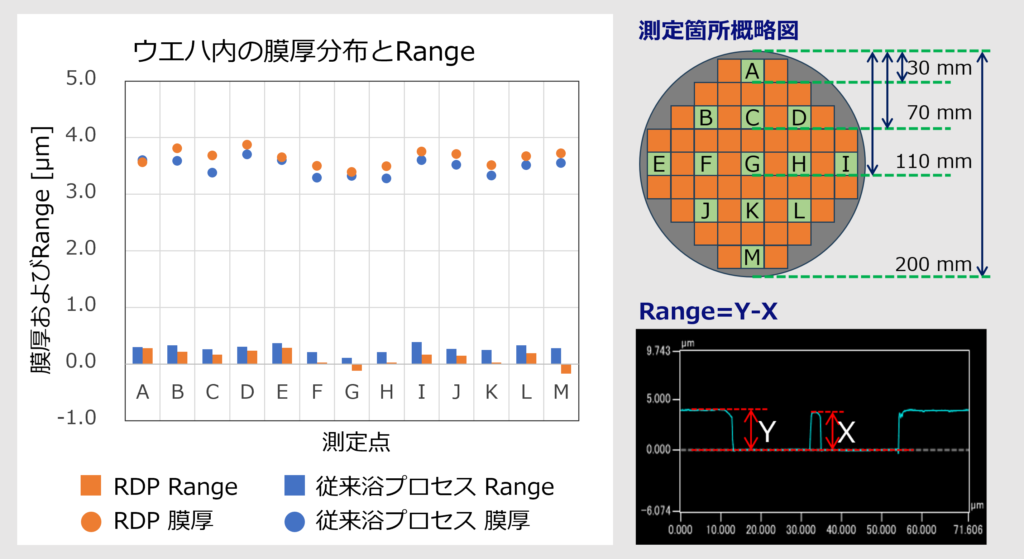

図1のグラフは8inchウエハ内の各測定点での配線膜厚とRangeを示している。RDPは従来プロセスに比べ、ウエハの各ユニット内でRangeが小さくなっていることが確認され、良好な面内均一性が得られている。

微細配線形成

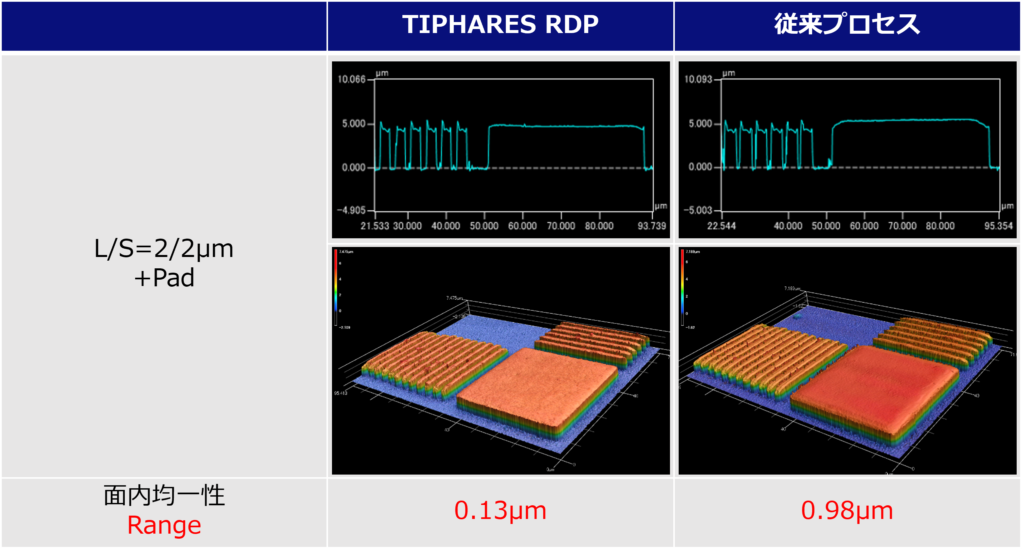

L/S=2/2μmの微細配線と40μm角のPadがデザインされた基材に対する、めっき評価の結果を図2に示す。

従来プロセスでは、Rangeが約1μmとなっているが、RDPはRangeが0.5μm以下となり、改善していることが確認できる。このようにRDPは膜厚差が生じやすい微細配線部に対しても良好な面内均一性を実現できる。

ビアフィリング性

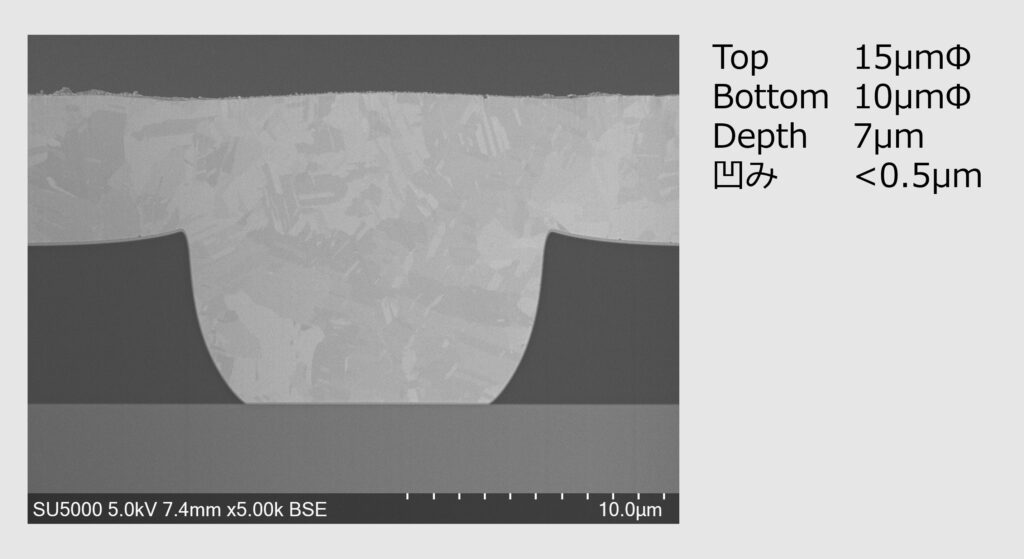

15μmφ-7μmdのBVHに対し、RDPでめっきを実施した断面SEM像を図3に示す。表層めっき膜厚が5μmにも関わらずBVHへのフィリング性が良好であることが確認できた。RDPは面内均一性が良好であるだけではなく、優れたビアフィリング性も有するプロセスである。

おわりに

TIPHARES RDPは優れたパターン面内均一性、微細配線の形成性能と、小径BVHへのビアフィリング性能を兼ね備えており、次世代半導体製造に必要とされるRDL Interposerに適したプロセスとなっている。