銅ピラー用高速硫酸銅めっきプロセス TIPHARES BUP(開発中)

総合研究所 電子技術開発部 下村 彩 Aya SHIMOMURA 鈴木 陽平 Yohei SUZUKI 鈴木 翔太 Shota SUZUKI

解析技術部 谷本 由美 Yumi TANIMOTO 小林 歩 Ayumu KOBAYASHI

はじめに

近年、半導体性能の向上を支えるAdvanced Package技術において、3次元(3D)実装と呼ばれるICチップを垂直方向に積層する構造が検討されている。その中には、200μmを超えるような厚膜の銅ピラーを形成しICチップ側への電源供給として使用する構造も検討されている。このような厚膜銅ピラーの形成に対し求められることとして、高生産性、高矩形性、高面内均一性が挙げられる。特に高生産性については、めっき時間の短縮が求められる。めっき時間の短縮は電流密度を上げることで見込まれるが、一般的に硫酸銅めっきでは電流密度に比例し、矩形性および面内均一性の低下が懸念される。

本稿では、高い電流密度において良好な矩形性および面内均一性を有する硫酸銅めっきプロセスTIPHARES BUPについて紹介する。

特長

- 10~50 ※A/dm²までの高電流密度で使用可能

- 銅ピラー形状に対する優れた矩形性

- 銅ピラー高さに対する良好な面内均一性

※撹拌・温度条件による

ハイアスペクト比デザインにおける銅ピラー形成

厚膜の銅ピラーにおいて、銅ピラーの膜厚とピラー径のアスペクト比は非常に重要である。3D実装におけるパッケージ基板設計において、銅ピラーの厚みはパッケージの厚みに対応しICチップの積層においては厚い方が望ましい。さらにピラーのピッチは高密度・高性能化により狭ピッチとなり、銅ピラー径は小さくなると予想される。そのため、銅ピラーをめっき形成する際の基材側のデザインは、フィルム(ドライフィルム等)の厚みが非常に厚く、開口径は小さいハイアスペクト比となるため、ハイアスペクト比のデザインへの銅ピラー形成が必須であると考える。

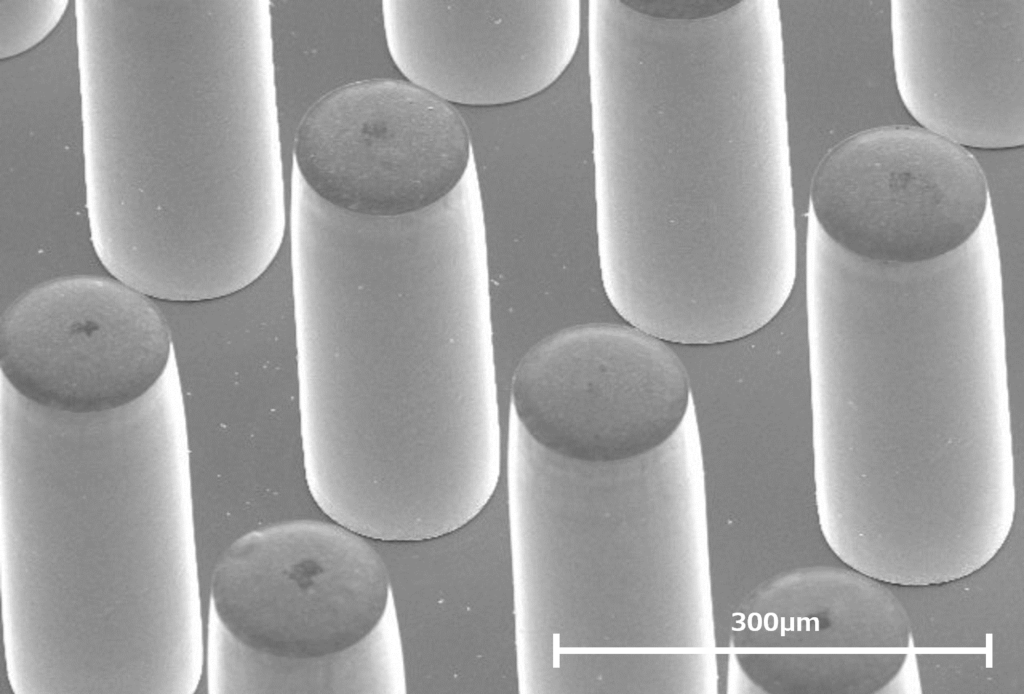

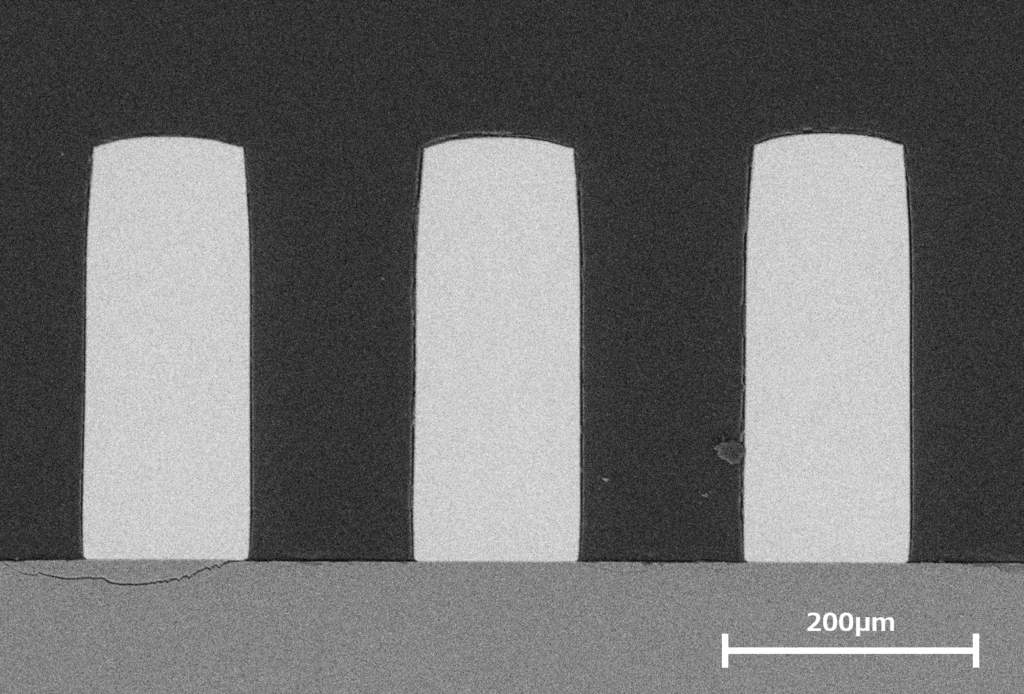

そこで、弊社ではアスペクト比2.7を超える、ドライフィルムレジスト厚340μm、開口径125μmのハイアスペクト比デザインに対しめっき加工を試みた。加工した際の走査型電子顕微鏡(SEM)にて撮影した鳥瞰画像を図1に、断面写真を図2に示す。

図1および図2の結果からハイアスペクト比のデザインにおいて、正常な析出および良好な矩形性であることが確認された。

[基材ご提供]

ドライフィルムレジスト:旭化成株式会社

露光機:株式会社オーク製作所

おわりに

TIPHARES BUPは、高い電流密度にて優れた面内均一性を実現した厚膜銅ピラーの形成を可能とし、ハイアスペクト比のデザインにおいて優れた矩形性を有しているプロセスである。