TSV用硫酸銅めっきプロセス TIPHARES TVP(開発中)

総合研究所 電子技術開発部 鈴木 翔太 Shota SUZUKI 長野 暢明 Nobuaki NAGANO

解析技術部 谷本 由実 Yumi TANIMOTO

はじめに

近年、High Performance Computing(HPC)市場で処理速度の高速化が求められる中、三次元集積回路(3D IC)の開発が積極的に取り組まれている。TSVはシリコンインターポーザやHigh Bandwidth Memory(HBM)などに用いられており、3D ICの重要性の高まりに伴い、TSV需要の増加が見込まれている。

本稿では、TSVに対して高速フィリングが可能な硫酸銅めっきプロセスTIPHARES TVPについて紹介する。

TSV

AIをはじめとしたテクノロジーの進化により、HPCの需要が拡大している。HPCを実現するには半導体デバイスの高集積化による性能向上が求められるようになった。

これらの対応策としてTSV接続を用いた3D ICの開発がより活発化に行われている。TSV接続により高集積化が可能となり、チップ間の接続距離が短くなることで高速処理および省電力化が可能となる。

TSVフィリング時間の短縮化

HPC市場の成長に伴い、TSVの生産量が増加傾向にあり、TSVめっきの時間短縮や歩留まり改善によるスループット向上が求められている。しかしながら、TSVフィリングのめっき時間短縮のために電流密度を増加させると、ビア内にボイドが発生する。ボイドが発生することで、接続信頼性の低下につながるため、ボイドの抑制は必要不可欠である。以上の理由から、めっき時間の短縮、フィリング性能および耐ボイド性の両立は、TSVの量産において重要な課題の一つとして挙げられる。

TIPHARES TVP(以下 TVP)は、従来プロセスより優れたフィリング性および耐ボイド性を有しながら、高電流密度に対応可能なプロセスであり、TSVの課題に応えるプロセスとなる。

特長

- 高速フィリングが可能

- ボイド抑制が可能

- 高アスペクトTSVに対応

フィリング性と耐ボイド性

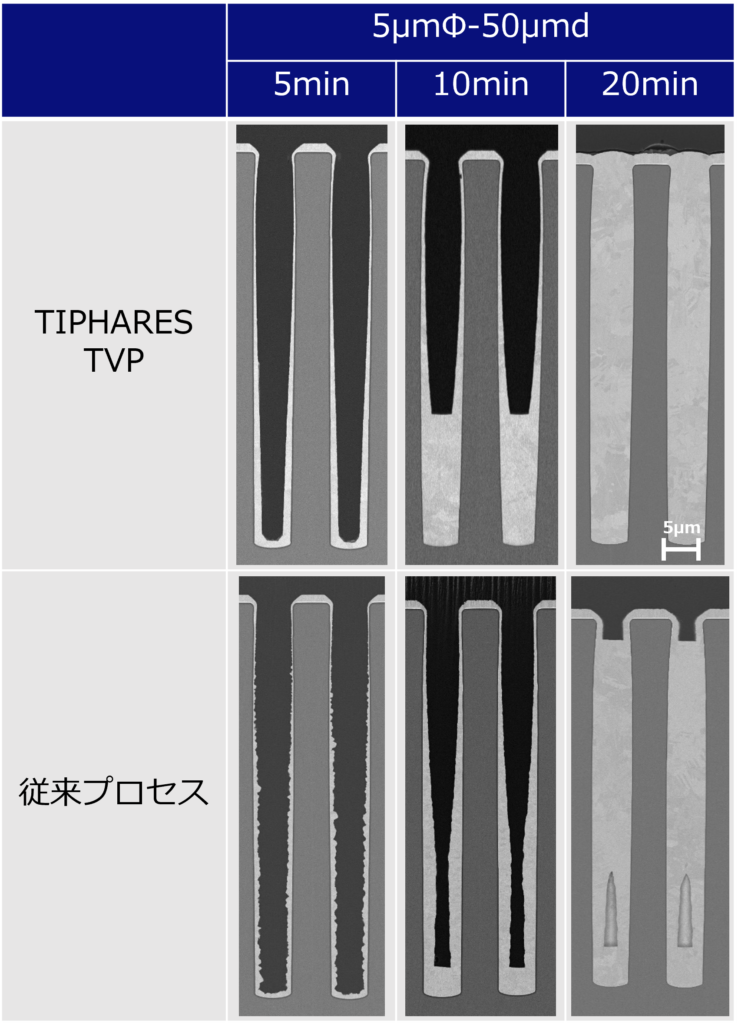

図1に従来プロセスとTVPの各時間におけるTSVフィリングめっき断面のSEM像を示す。図1の結果から、高電流密度で加工した際の従来プロセスでは、TSV底部付近からボイドの発生を確認した。

これに対してTVPは、22minでボイドレスかつ良好なフィリングを達成した。これらの結果から、TVPは、高電流密度を用いた場合でもボイドを抑制しつつ、TSV内部のボトムアップを促進することで高速フィリングが可能である。

0.4A/dm², 5, 10,22 min

おわりに

TIPHARES TVP は従来プロセスより、高い電流密度において、優れたフィリング性と耐ボイド性を有している。これらの特徴より、TSVフィリングの歩留まりを改善し、生産量の向上とコストの削減が可能となることから、最先端実装技術への貢献が期待される。