ウエハー用高速銅ピラーめっきプロセス(開発中) CU-BRITE BU3

総合研究所 電子技術開発部 下村 彩 Aya SHIMOMURA 鈴木 翔太 Shota SUZUKI

森川 竜汰 Ryuta MORIKAWA

CS電子技術部 福田 耀大 Kouta FUKUDA

解析技術部 岸本 一喜 Kazuki KISHIMOTO

はじめに

近年、最先端パッケージとして注目が集まる半導体実装技術の1つとして、Fan-Out Wafer-Level Package(以下、FO-WLP)を利用した積層技術がある。Cuピラーは、FO-WLPなどを積層する際のインターコネクトとして用いられ、放熱性や信号特性向上の観点から需要の増加が見込まれている。

本稿では、高速でCuピラーの形成が可能なプロセスCU-BRITE BU3(以下、BU3)について紹介する。

Cuピラー

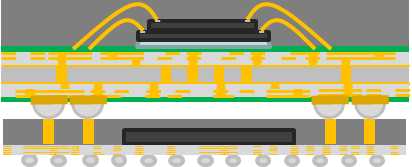

主にモバイル向けの実装技術として、半導体パッケージを積層するPackage On Package(以下、PoP)という技術がある。パッケージを垂直方向に重ねることにより水平方向に並べるよりも省スペース化が実現できる。また、パッケージ同士の接続配線も短くなるため、シグナル損失の低減も期待されている。近年、一部のハイエンドモバイル端末ではFO-WLP構造を使用したPoPが採用されており、その接続部にはCuピラーの形成が必要とされている(図1)。

Cuピラーは高密度化やチップの三次元実装などに伴い、狭ピッチ化や厚膜化が予想され、厚膜Cuピラー(以下、メガピラー)が求められている。また、メガピラーの形成時の要求性能として、形成処理時間の短縮のための「高生産性」、後工程のコスト削減につながる「高矩形性」「高面内均一性」の3点が挙げられる。

Cuピラー形成処理時間の短縮化

高電流密度でめっき処理を行うことにより、Cuピラー形成時間を短縮することができる。しかしながら、一般的に硫酸銅めっきでは電流密度に比例し、矩形性および面内均一性の低下が懸念される。そのため、処理時間の短縮と性能の両立は困難であり、メガピラー形成においても大きな課題と考えられる。

BU3は、優れた矩形性および面内均一性を有しながら、高電流密度に対応可能であり、Cuピラー形成処理時間の短縮化を実現したプロセスである。

特長

- 10~25A/dm²の高電流密度で使用可能

- Cuピラー形状に対する優れた矩形性

- Cuピラー高さに対する良好な面内均一性

矩形性および面内均一性

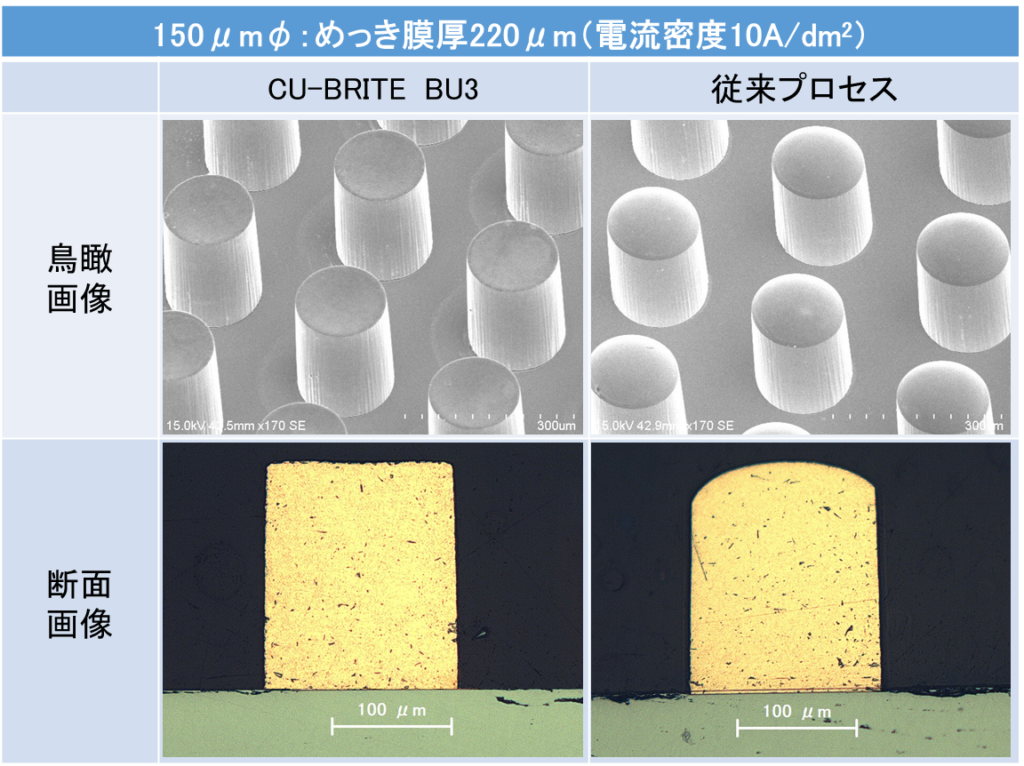

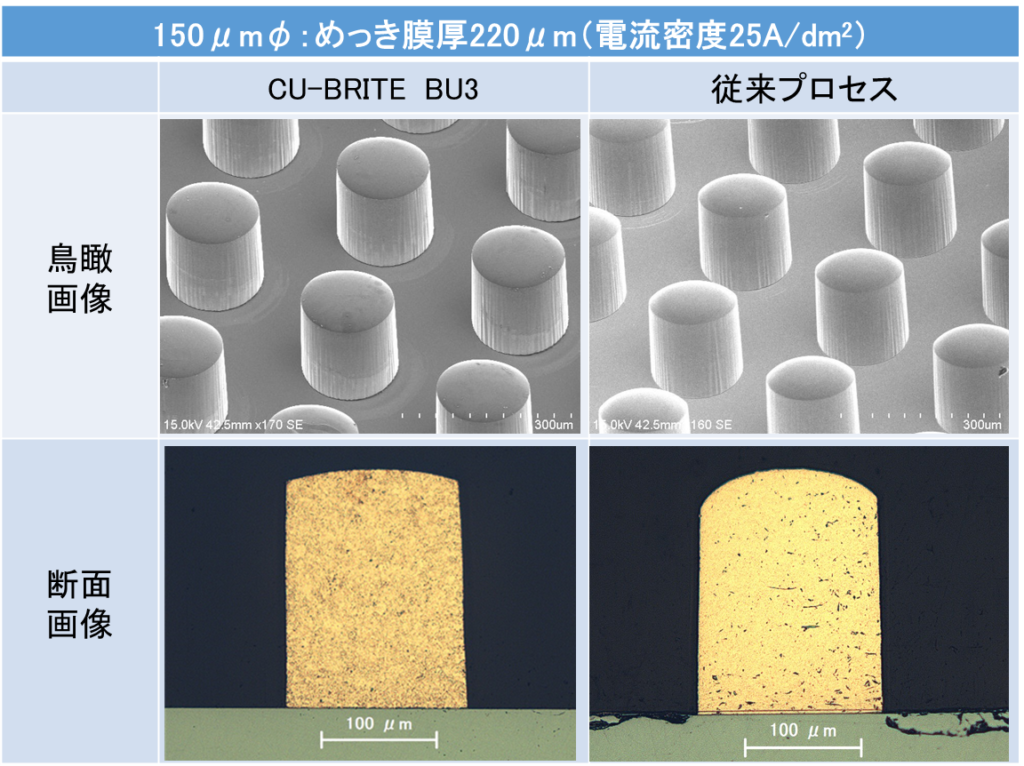

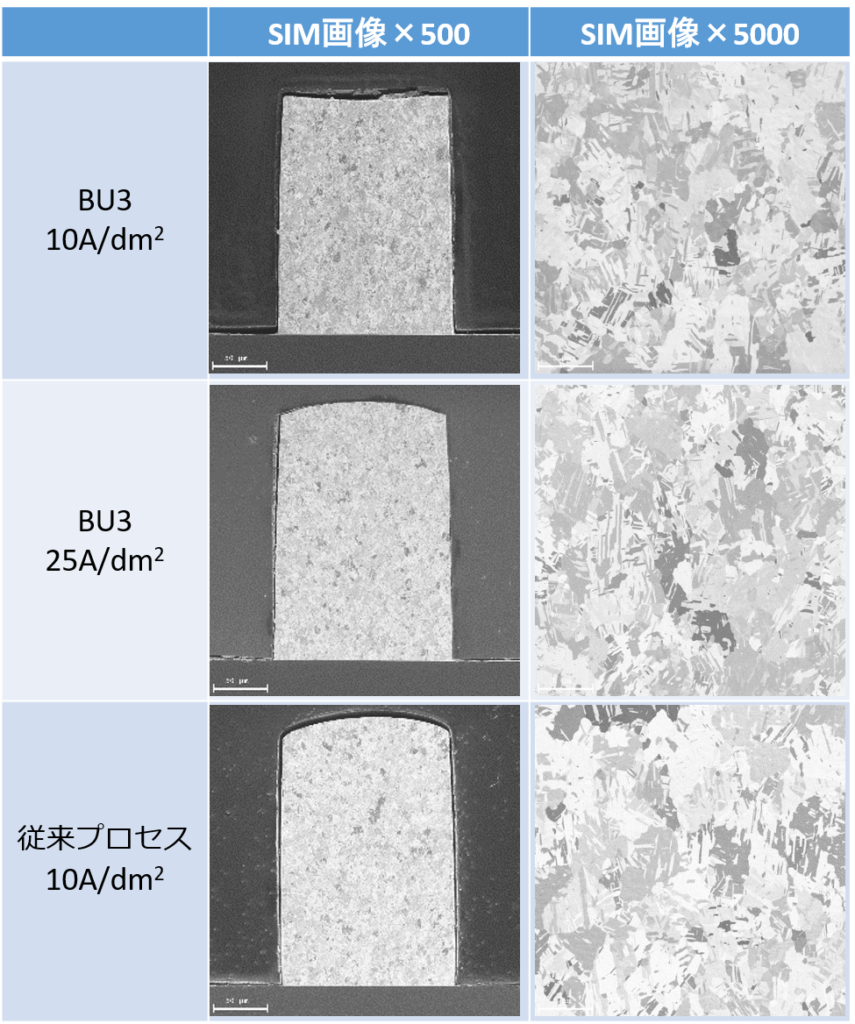

図2、3にCuピラー形状の鳥瞰画像および断面画像を示す。形成時の電流密度は10および25A/dm²である。図2、3の結果から、従来プロセスと比較して矩形性に優れたCuピラーが得られることが確認できた。

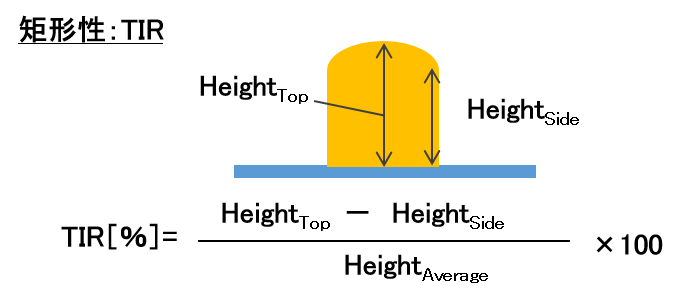

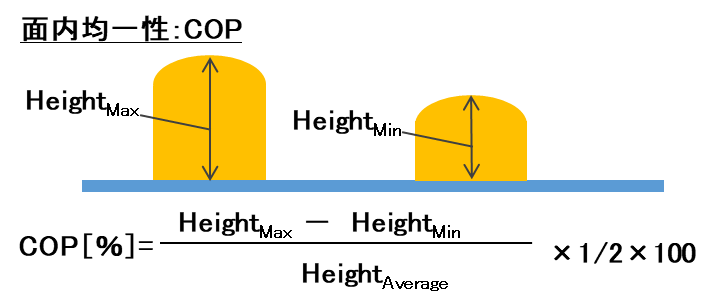

図4、5にCuピラーの評価項目である矩形性および面内均一性の測定方法を示す。矩形性はTotal Indicated Runout( 以下、TIR)で計測しており、TIRは正の値がドーム型、負の値がディッシュ型となり、ゼロの値に近いほど、優れた矩形性を示す。面内均一性(Co-planarity:以下、COP)に関しては、WID計算方法で算出しており、TIR同様にゼロの値に近いほど優れた面内均一性を示す。

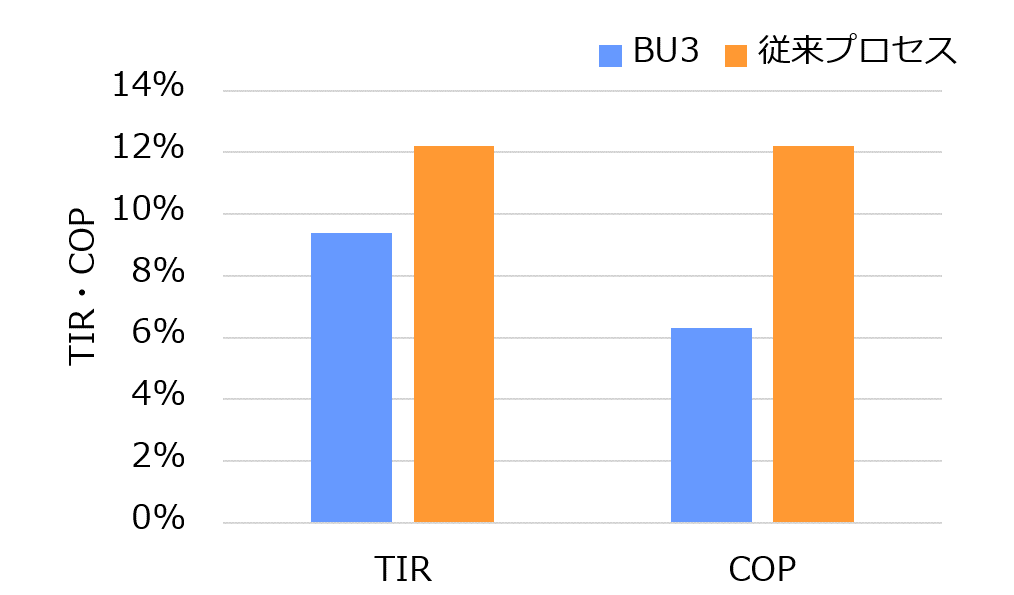

図6に電流密度25A/dm²における矩形性および面内均一性の性能比較を示す。矩形性は、従来プロセスがTIR12%の凸形状になっていることに対してBU3は9%となりTIR10%以下を達成した。またCOPに関してもTIR同様に従来プロセスが12%に対し、およそ半分の6%まで改善することが確認でき、COP10%以下を達成した。

Cuピラーの結晶状態

図7に電流密度10および25A/dm²におけるCuピラーのSIM画像を示す。図7の結果から、10A/dm²では従来プロセスとBU3を比べ結晶状態に大きな違いはないことが確認できた。また、BU3の10A/dm² と25A/dm²の結晶状態を確認した結果、電流密度の違いにおいても大きな違いはないことが確認できた。

おわりに

CU-BRITE BU3は、従来プロセスで困難であった高電流密度によるCuピラー形成を可能とし、優れた矩形性と面内均一性を有している。めっき性能の向上により、高生産性の実現や後工程のコスト削減が期待できる。