Library JCUライブラリ

ネプコン展示会のお知らせ

JCUについて

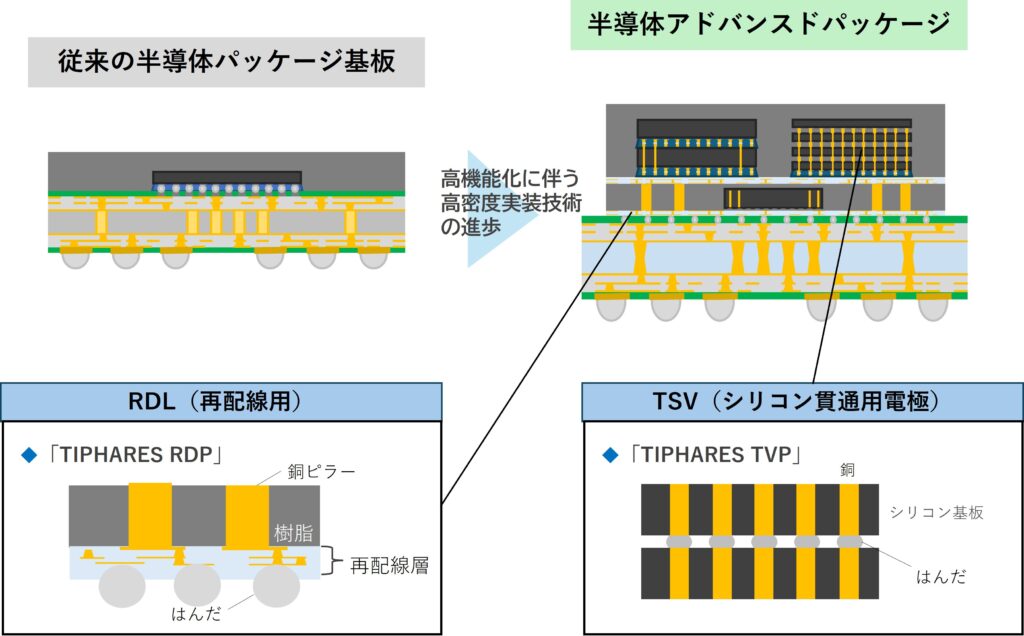

このたび弊社は、2025年1月22日から24日にかけて、ネプコンジャパンに出展することとなりました。当展示会では、前回のSEMICON Japan2024/APCSに引き続き、「TIPHARES(ティファレス)」シリーズの展示を予定しております。開催を控え、今回は新しく開発中の「TIPHARES TVP」に加え、既に拡販中である再配線層向け硫酸銅めっきプロセスの「TIPHARES RDP」についてご紹介いたします。

① TIPHARES TVP

「TIPHARES TVP」はTSV用の硫酸銅めっきプロセスです。TSV(Through-Silicon Via)とは、シリコン貫通電極のことを指します。従来はワイヤーボンド※1により半導体チップ※2を電気的に接続していました。TSVではその代わりに、シリコンウエハや半導体チップに垂直に貫通する穴を直接開け、その中を金属でフィリング(埋める)することで電極を作り、接続を行います。接続距離が短くなることで、配線の高密度化や電気信号の高速化が可能となり、デバイスの性能向上が期待される技術です。現在はHBM※3等に多く活用され、今後も3次元パッケージの普及と共に需要が高まると予測されます。

「TIPHARES TVP」の特長は、①高速フィリング※4②耐ボイド性③高アスペクトTSVに対応の3点が挙げられます。

現在市場の成長に伴い、TSV用の硫酸銅めっきは単位時間当たりの生産能力の向上が要求されています。生産量増加のためには、電流密度を高くして短時間でのめっきを行う必要があります。しかし、硫酸銅めっきは高い電流密度で行うとめっきの被膜が不均一になりやすく、高電流密度下では「ボイド(void)」と呼ばれるめっき被膜の中の空洞や欠陥も生じやすくなります。これらは電気接続に問題が起こる原因となり、最終製品の品質に影響を与えます。これらTSV用の硫酸銅めっきの技術的課題に対し、「TIPHARES TVP」は優れたフィリング性と耐ボイド性を両立しており、半導体チップ製造における生産性が改善されたプロセスとなっています。さらに、高アスペクト比(配線の深さと直径の比が大きく、細長い形状)を有するため、配線の高密度化に適した薬品となっています。

② TIPHARES RDP

「TIPHARES RDP」は再配線層向けの硫酸銅めっきプロセスです。再配線層(Redistribution Layer:以下、RDL)とは、非常に小さく密集した半導体チップの配線の位置を整理して配線を引き直し、外部と接続するための層です。近年電子デバイスの小型化・高性能化による半導体の微細化技術が進む中、複数の半導体チップを1つのパッケージに搭載する技術の需要が高まっています。その流れの中、検討が進む他の技術と比べ、比較的安価で電気特性の良いRDLインターポーザー※5が注目されています。

「TIPHARES RDP」の特長として、①良好な面内均一性※6②BVH※7への高いフィリング性の2つが挙げられます。RDLインターポーザーは配線幅やBVH(ブラインドビアホール)が極めて微細になり、高いフィリング性が求められます。さらには、再配線層を積層する際に面内均一性が低いと電気の接続信頼性が低下する恐れがあることから、高い面内均一性も合わせて要求されます。「TIPHARES RDP」はこれらの課題に対し、良好な面内均一性とBVHへの高いフィリング性を保持することで、RDLインターポーザーに要求されるめっきの技術的要求を満たす薬品となっています。

「TIPHARES」シリーズは、次世代半導体を製造する技術である半導体アドバンスドパッケージ※8向けの製品です。弊社は、電子機器の高機能化に伴うめっき技術のニーズの変化に対応し、今後も次世代領域製品の開発を強化してまいります。上記でご紹介した他にも、複数の製品ラインナップの展示を行っておりますので、この機会にぜひご来場ください。

※1 ワイヤーボンド…金属ワイヤーを用いて半導体チップと外部部品を繋ぐ技術

※2 半導体チップ… メモリやロジックIC(集積回路)などを組み合わせてパッケージングされた半導体集積回路の総称

※3 HBM…従来よりも高いデータ転送速度を実現するための3D積層メモリのこと

※4 フィリング…電気を流せるようにするために、基板に開いた穴に銅を充填すること

※5 RDLインターポーザー…再配線層において、半導体チップと基板を電気的に繋ぐ仲介役となる部品

※6 面内均一性…基板全体に対し、めっきの膜厚が均一であること

※7 BVH…層同士を銅配線で接続するための表面層から中間層まで空いた穴のこと

※8 半導体アドバンスドパッケージ…半導体における微細化技術の限界を克服するために複数の半導体チップを組み合わせてひとつのパ

ッケージにするための技術

第39回ネプコンジャパン

- 会期

-

2025年1月22日(水)~1月24日(金)

- 会場

-

東京ビッグサイト東7ホール

- ブース番号

-

E64-8

<第39回 ネプコン ジャパン -エレクトロニクス 開発・実装展->公式サイト

https://www.nepconjapan.jp/tokyo/ja-jp/visit.html

※来場登録はこちらからよろしくお願いいたします。

本件の問い合わせ先

株式会社 JCU 経営戦略室 経営企画部

TEL:03-6895-7004 E-mail:kikaku@jcu-i.com